一、引言:集成電路設(shè)計(jì)全景概覽

集成電路(IC)設(shè)計(jì)是一個復(fù)雜且精密的過程,通常分為前端設(shè)計(jì)和后端設(shè)計(jì)兩大核心階段。前端設(shè)計(jì)聚焦于芯片的邏輯功能、架構(gòu)定義和寄存器傳輸級(RTL)設(shè)計(jì),而后端設(shè)計(jì)則是將前端輸出的邏輯網(wǎng)表轉(zhuǎn)化為可用于制造的物理版圖(GDSII文件)的關(guān)鍵環(huán)節(jié)。隨著半導(dǎo)體工藝節(jié)點(diǎn)不斷演進(jìn)至納米級別,后端設(shè)計(jì)的復(fù)雜性和重要性日益凸顯,成為決定芯片性能、功耗、面積(PPA)和最終上市時間(Time-to-Market)的決定性因素。本課件旨在系統(tǒng)介紹集成電路后端設(shè)計(jì)的基本流程、核心技術(shù)及其在整體芯片設(shè)計(jì)與服務(wù)生態(tài)中的角色。

二、集成電路后端設(shè)計(jì)核心流程

后端設(shè)計(jì)是一個多步驟、迭代優(yōu)化的物理實(shí)現(xiàn)過程,主要包括以下階段:

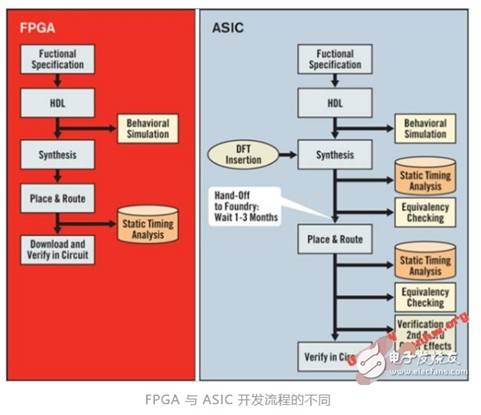

- 邏輯綜合與可測性設(shè)計(jì)插入:使用綜合工具將RTL代碼轉(zhuǎn)換為基于目標(biāo)工藝庫的門級網(wǎng)表。為了確保芯片的可測試性,會插入掃描鏈(Scan Chain)等DFT(Design for Test)結(jié)構(gòu)。

- 布圖規(guī)劃與電源規(guī)劃:

- 布圖規(guī)劃:確定芯片核心區(qū)域(Core Area)、輸入輸出(I/O)單元、宏模塊(如存儲器、IP核)的擺放位置,為后續(xù)布局布線提供基礎(chǔ)框架。目標(biāo)是優(yōu)化芯片面積、信號完整性和時序性能。

- 電源規(guī)劃:設(shè)計(jì)全局和局部電源/地線網(wǎng)絡(luò),確保整個芯片供電均勻、穩(wěn)定,壓降(IR Drop)和電遷移(EM)符合要求。

- 布局:將綜合后的標(biāo)準(zhǔn)單元(Standard Cell)放置到芯片核心區(qū)域內(nèi)。需考慮單元間的連接關(guān)系、時序路徑、擁塞程度和功耗分布,進(jìn)行初步優(yōu)化。

- 時鐘樹綜合:構(gòu)建一個低偏斜(Skew)、低功耗的全局時鐘分布網(wǎng)絡(luò),確保時鐘信號能同步、可靠地送達(dá)所有時序單元(如觸發(fā)器)。這是影響芯片性能和穩(wěn)定性的關(guān)鍵步驟。

- 布線:根據(jù)邏輯連接關(guān)系,在多層金屬互連層上完成所有標(biāo)準(zhǔn)單元、宏模塊和I/O單元之間的物理連接。需解決信號完整性(如串?dāng)_)、設(shè)計(jì)規(guī)則檢查(DRC)和電氣規(guī)則檢查(ERC)等問題。

- 物理驗(yàn)證與簽核:

- 物理驗(yàn)證:對最終版圖進(jìn)行嚴(yán)格的DRC、LVS(版圖與原理圖一致性檢查)和ERC檢查,確保其符合晶圓廠的制造規(guī)則。

- 簽核分析:進(jìn)行最終、最精確的時序分析(STA)、功耗分析、信號完整性分析和可靠性分析(如EM/IR),確保設(shè)計(jì)在所有工藝角(Corner)和環(huán)境下都能滿足性能、功耗和可靠性指標(biāo)。

- 流片數(shù)據(jù)準(zhǔn)備:生成最終交付給晶圓廠進(jìn)行光刻制造的GDSII格式版圖文件及相關(guān)文檔。

三、后端設(shè)計(jì)中的關(guān)鍵技術(shù)挑戰(zhàn)與趨勢

- 先進(jìn)工藝挑戰(zhàn):在7nm、5nm及以下節(jié)點(diǎn),物理效應(yīng)(如短溝道效應(yīng)、量子隧穿)和工藝變異(PVT)的影響加劇,對時序收斂、功耗管理和可靠性設(shè)計(jì)提出極致要求。

- 多物理場協(xié)同優(yōu)化:需要同時考慮電學(xué)、熱學(xué)、力學(xué)等多物理場效應(yīng),進(jìn)行電熱協(xié)同、熱電協(xié)同等分析優(yōu)化。

- 人工智能與機(jī)器學(xué)習(xí)應(yīng)用:AI/ML技術(shù)正被用于加速布局、預(yù)測擁塞和優(yōu)化PPA,實(shí)現(xiàn)設(shè)計(jì)空間探索的自動化和智能化。

- Chiplet與先進(jìn)封裝:隨著Chiplet(芯粒)和2.5D/3D集成電路技術(shù)的發(fā)展,后端設(shè)計(jì)范疇擴(kuò)展至硅中介層、微凸塊和硅通孔(TSV)的設(shè)計(jì)與協(xié)同,涉及系統(tǒng)級封裝(SiP)的物理實(shí)現(xiàn)。

四、集成電路芯片設(shè)計(jì)服務(wù)生態(tài)

專業(yè)的集成電路設(shè)計(jì)服務(wù)公司或部門,提供從前端到后端的全流程或部分流程外包服務(wù)(如Turnkey或NRE模式),其服務(wù)價值體現(xiàn)在:

- 專業(yè)分工與效率提升:讓芯片設(shè)計(jì)公司(Fabless)能專注于核心架構(gòu)與算法,將復(fù)雜、工具依賴度高的物理實(shí)現(xiàn)交由專業(yè)團(tuán)隊(duì),縮短開發(fā)周期。

- 技術(shù)積累與資源共享:服務(wù)商積累了跨工藝、跨應(yīng)用的豐富設(shè)計(jì)經(jīng)驗(yàn)、IP庫和設(shè)計(jì)方法論,能有效規(guī)避設(shè)計(jì)風(fēng)險。

- 成本優(yōu)化:通過優(yōu)化PPA,幫助客戶降低芯片的制造成本和使用成本,提升產(chǎn)品競爭力。

- 全生命周期支持:服務(wù)不僅限于設(shè)計(jì)實(shí)現(xiàn),還可能涵蓋設(shè)計(jì)咨詢、IP集成、流片支持、封裝測試協(xié)同乃至量產(chǎn)后的良率提升支持。

五、

集成電路后端設(shè)計(jì)是將抽象邏輯轉(zhuǎn)化為物理現(xiàn)實(shí)的橋梁,是確保芯片性能、可靠性和可制造性的核心環(huán)節(jié)。面對日益復(fù)雜的工藝和系統(tǒng)集成需求,后端設(shè)計(jì)技術(shù)持續(xù)演進(jìn),并與設(shè)計(jì)服務(wù)生態(tài)緊密結(jié)合,共同推動著全球半導(dǎo)體產(chǎn)業(yè)的創(chuàng)新與發(fā)展。掌握后端設(shè)計(jì)的核心流程與挑戰(zhàn),對于芯片設(shè)計(jì)工程師、項(xiàng)目管理者及產(chǎn)業(yè)投資者都至關(guān)重要。